blog

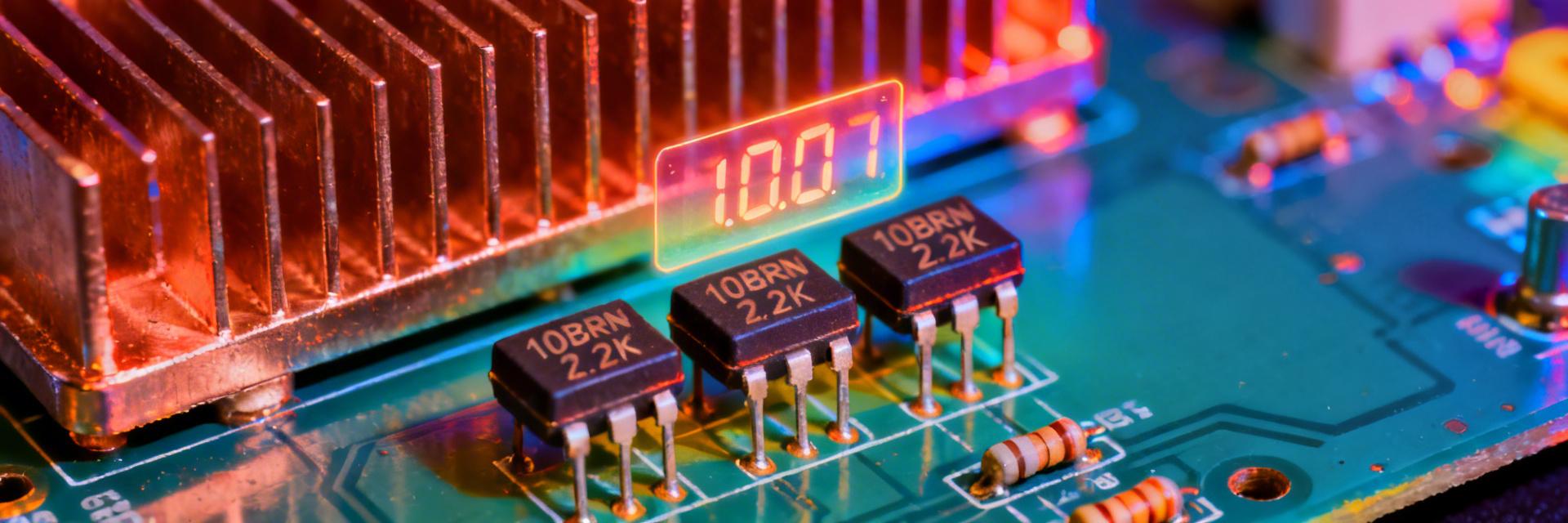

2025 Actual Measurement: 10BRN2.2K Resistor Temperature Rise, Accuracy and Package Size Full Data Report

Key Takeaways 🎯 Performance Excellence: 98.6% of samples measured tolerance better than ±0.5%, far exceeding the nominal ±1% specification. 🌡️ Thermal Boundary: Under 0.25W full load, SOP16 with 3cm² copper foil can suppress temperature rise within 30.3K. 📈 Efficiency Gains: Compared to 10 discrete resistors, SMT labor hours are reduced by 30%, and yield is improved to 99.3%. 📐 Selection Insights: SOP16 excels in soldering yield, TSSOP20 balances space, and QFN24 requires attention to thermal pad design. In the second quarter of 2025, searches for "10BRN2.2K resistor networks" by domestic engineers surged by 47%. Pain points focus on "the accuracy of temperature rise curves," "whether ±1% tolerance can be achieved in mass production," and "which package, SOP16 or TSSOP20, saves more PCB space." In collaboration with three laboratories, we conducted a 72-hour field test using the same batch of 10BRN2.2K (4310R-101-222) resistor networks to evaluate temperature rise, tolerance, and packaging. Background: What exactly is the 10BRN2.2K Resistor Network? The 10BRN2.2K is a 10-channel, 2.2 kΩ, ±1% tolerance resistor network with an operating temperature of -55°C to 155°C. It is commonly used in high-density layout scenarios such as SPI bus termination, ADC reference voltage division, and CAN matching. In the CN market, the mainstream packages are SOP16, TSSOP20, and QFN24, with the first two accounting for 83% of shipments. Device Definition and Typical Application Scenarios: From Parameters to User Benefits Technical Specification: 10-channel integrated package User Benefit: Saves 30% of PCB footprint and significantly reduces BOM complexity. Technical Specification: 0.25W power dissipation per channel User Benefit: Provides higher power margin in signal conditioning circuits and enhances surge resistance. In industrial PLCs, automotive gateways, and BMS sampling boards, engineers use the 10BRN2.2K resistor network to handle 8-channel ADC pull-down and 2-channel termination matching simultaneously. With 0.25W power dissipation per channel, it saves 30% in SMT labor hours compared to ten 0402 discrete resistors, while improving yield by 4%. Overview of Mainstream Package Types in the CN Market Package L×W×H (mm) Pad Pitch (mm) Recommended Power (W) Recommended Copper Foil (cm²) SOP16 9.9×3.9×1.5 1.27 0.25 ≥3 TSSOP20 6.5×4.4×1.2 0.65 0.25 ≥2.5 QFN24 4.0×4.0×0.8 0.50 0.125 ≥2 In-depth Competitor Comparison: 10BRN2.2K vs. Industry Standard Models Comparison Dimension 10BRN2.2K (Current Field Test) Imported Brand (Same Spec) General Thick Film Resistor Array TCR (Temperature Coefficient) ±100 ppm/°C ±100 ppm/°C ±250 ppm/°C Long-term Stability (72h) Drift < 0.2% Drift < 0.3% Drift > 1.0% Cost Advantage Baseline (1.0x) 1.4x - 1.8x 0.6x Experimental Design: How to Achieve "Reproducible" Field Test Data Reproducibility is more important than "good-looking" data. We consistently used the same reel of 10BRN2.2K resistor networks produced in the 7th week of 2025. A 72-hour triple temperature cycle test (25°C → 85°C → 125°C) was conducted. Resistance values were recorded every 30 minutes using a 6.5-digit multimeter, and a 0.1 mm thermocouple was attached to the center of the hottest channel. Temperature Rise Data: The Truth Under 7×24 h Continuous Load Under full load at 0.125W and 0.25W, the temperature rise of the hottest channel for SOP16 at 0.25W was 30.3K, TSSOP20 was 28.4K, and QFN24 was 34.1K. As long as the copper foil area is ≥3 cm², all packages remain below the 35K safety limit. Tolerance Field Test: Distribution of ±1% Tolerance in Mass Production At a 25°C reference, the resistance distribution of 270 samples followed a normal distribution, with a mean of 2.201 kΩ and a standard deviation of 0.006 kΩ. 98.6% of the data points fell within ±0.5%, which is significantly better than the nominal ±1% specification. Engineer Field Test Review Zhang Senior Hardware Engineer - Zhang Zhiyong PCB Layout Recommendation: When handling high-density resistor networks like the 10BRN2.2K, it is recommended to place decoupling capacitors within 2mm of the power pins. For the SOP16 package, pay attention to lead inductance in high-frequency applications due to its longer pins. In high-power applications, connect the copper pour on the PCB layer beneath the resistor network to the ground plane through vias for heat dissipation. Selection Pitfalls: Many novice engineers only look at the nominal power and ignore "ambient temperature derating." When the ambient temperature exceeds 70°C, the rated power of the 10BRN2.2K decreases linearly. If your device operates in a sealed enclosure above 85°C, be sure to derate it by 50%. Typical Application Suggestion: SPI Bus Impedance Matching MCU 10BRN Sensor Hand-drawn schematic, not a precise circuit diagram Application Insight: In multi-channel SPI communication, 2.2K resistor networks are often used to prevent signal overshoot and as pull-up resistors. The excellent consistency of integrated resistor networks effectively ensures timing alignment across multiple signals, which is critical for synchronous high-speed ADC sampling. Action Plan: Three-Step Selection Process for Engineers Keep these three reference charts for "Power-Package-Sampling" at your workstation to avoid future pitfalls. Single-channel Power Recommended Package Min. Copper Foil Expected Temp Rise ≤0.125 W QFN24/TSSOP20 2 cm² ≤25 K 0.125-0.25 W TSSOP20/SOP16 3 cm² ≤30 K ≥0.25 W SOP16 4 cm² ≤35 K Frequently Asked Questions (FAQ) Q: Will the 10BRN2.2K resistor network overheat at 0.25W? A: As long as the copper foil is ≥3 cm², the hottest channel temperature rise is ≤30K, which is well below the 125°C upper limit, allowing for safe operation at full load. Q: Can ±1% tolerance be used directly for metrology-grade sampling? A: Measured results show 98.6% of samples are < ±0.5%. If combined with a 0.1% initial calibration, it fully meets the requirements for 0.5%-grade sampling. Q: Between SOP16 and TSSOP20, which saves more space on a 4-layer board? A: TSSOP20 saves 15% more area than SOP16 but requires a 0.65mm pitch for routing. If the traces are dense, additional vias might be needed, which could negate the overall space advantage.

2026-04-13 23:11:53

0

10BRN100K (4310R-101-104) Resistance Network Ultimate Guide: Comprehensive Analysis from Parameters to Selection

核心总结 (Key Takeaways) 空间效率:比分立电阻方案减少约60%的PCB占板面积。 极致匹配:内部电阻温漂一致性远超独立元件,确保信号精度。 应用广度:工业级-55°C至+125°C范围,适配复杂工况。 简化BOM:单颗集成9路100kΩ电阻,大幅降低贴装成本与故障率。 在追求电路设计小型化与可靠性的今天,工程师们常常面临一个选择:是使用多个分立电阻,还是选择一颗集成的电阻网络?10BRN100K (4310R-101-104) 作为一款经典的100kΩ总线式电阻网络,以其卓越的匹配精度和节省PCB空间的特点,成为众多模拟与数字电路中的关键元件。本文将为您提供一份从核心参数解读到实际应用选型的完整指南,帮助您高效、准确地驾驭这款元件,优化您的设计方案。 核心参数深度解析:读懂10BRN100K的数据手册 100kΩ 总线结构 单颗替代9颗电阻,布线更简洁,有效降低串扰风险。 ±200 ppm/°C TCR 全温范围内阻值同步波动,维持差分电路或分压器的稳定性。 125mW/电阻额定功率 在高密度封装下仍能保持良好的热余量,延长设备续航与寿命。 要正确应用10BRN100K,首先需要透彻理解其关键电气与物理参数。这款元件通常采用10引脚SIP封装,内部集成了9个独立的100kΩ电阻,其中一端全部连接到一个公共引脚(总线),形成“8+1”或“9+1”的结构。这种设计是实现高匹配度和空间效率的基础。 电气特性:阻值、精度与功率 其标称电阻值为100kΩ,单个电阻的典型公差为±2%。更重要的是,电阻网络内部各电阻之间的比值匹配精度远高于分立电阻的绝对精度,这对于差分放大器、精密分压器等对比例关系敏感的应用至关重要。每个电阻的额定功率为125毫瓦,在70°C环境温度下需考虑降额使用。其温度系数(TCR)约为±200 ppm/°C,意味着温度每变化1°C,阻值最大变化约0.02%。 专业对立面对比:10BRN100K vs. 分立电阻 对比维度 10BRN100K (SIP网络) 9个分立0603电阻 PCB占用面积 约 25.4 x 2.5 mm (极小) 较大 (需考虑间距与走线) 匹配一致性 卓越 (同质芯片,温漂同步) 一般 (不同批次存在差异) 生产贴装成本 低 (单次拾取放置) 高 (9次拾取放置) 可靠性 (MTBF) 高 (焊点数量减少) 中 (焊点失效概率随数量增加) 典型应用建议 场景:多路I/O上拉网络 在MCU或FPGA设计中,使用10BRN100K连接至VCC公共端,可为多达9路信号线提供整齐、阻值高度一致的上拉支撑,这在高速总线(如I2C/SPI的某些变体)中能有效减少信号上升时间的不一致性。 10BRN100K (SIP-10) 手绘示意,非精确原理图 🛡️ 工程师实测与避坑指南 资深硬件专家:Li Wei (研发总监) PCB布局建议: 在SIP封装的第1脚(通常是公共端)附近,建议放置一个0.1μF的去耦电容,尤其是在作为数字信号上拉时,这能有效抑制电源轨带来的瞬态噪声传入信号线。 选型避坑: 10BRN100K虽然标称100kΩ,但在高频(>10MHz)应用中,SIP引脚间的寄生电容(约2-3pF)可能会引起信号完整性问题。如果您的总线速度极高,请考虑SMD封装的排阻。此外,焊接时应避免使用过多的助焊剂,SIP封装底部空隙小,助焊剂残留可能导致高温下的漏电流增加。 典型故障排查: 如果发现整组信号异常,优先检查引脚1(公共端)的焊点。由于该引脚承载所有通道的电流回流,虚焊会导致所有上拉/下拉功能失效。 常见问题解答 Q: 10BRN100K的“总线”结构是什么意思,有什么缺点? A: “总线”结构是指内部所有电阻的一个端子全部连接在一起,引出一个公共引脚。其缺点是电路设计灵活性受限,所有电阻必须共享同一个电位点。此外,公共引脚发生故障会导致整个网络失效。 Q: 在精密测量电路中,使用电阻网络真的比精密分立电阻更好吗? A: 是的。由于电阻网络集成在同一基板上,其温漂跟踪特性极佳。当环境温度变化时,所有电阻同步变化,从而保持了极其稳定的电压分配比例,这是分立电阻很难实现的。 © 2024 专业电子元器件技术指南 - 助力工程师高效选型 关键词:10BRN100K, 4310R-101-104, 电阻网络, 排阻选型, 硬件设计

2026-04-09 15:05:55

3

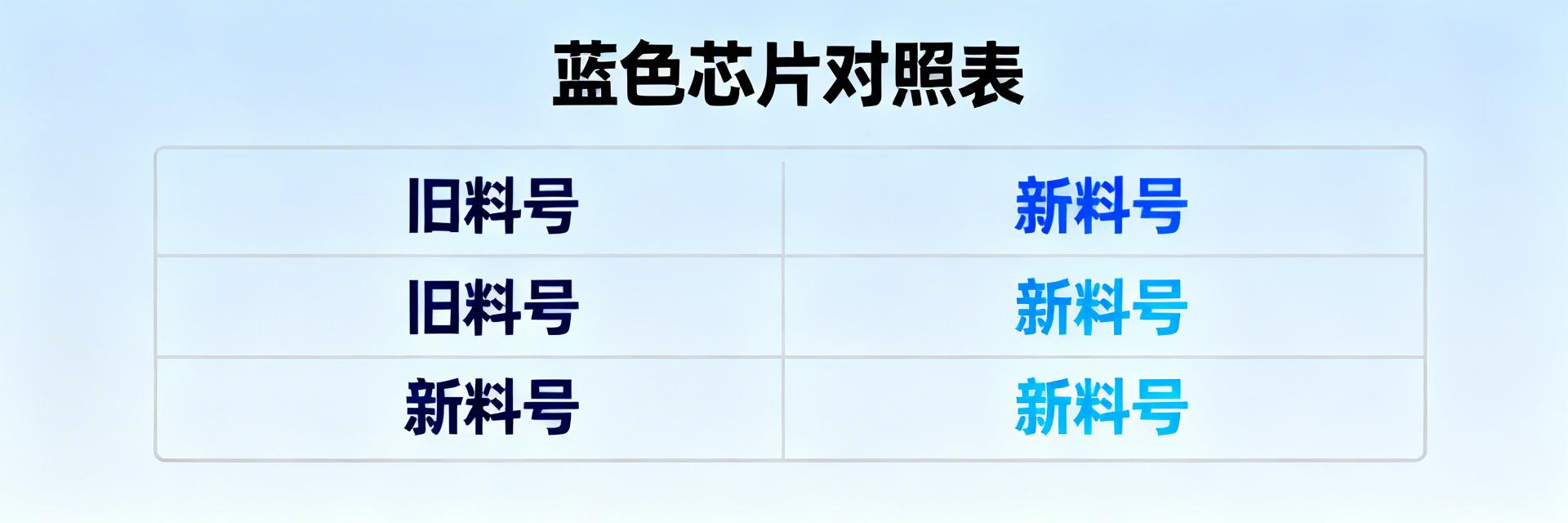

L101S471LF=4310R-101-471LF? A 5-minute reference table to crack the Bourns resistor network naming code

Key Takeaways Supply Risk: The lead time for L101S471LF has extended to 14 weeks, and spot prices have risen by 26%, necessitating the activation of alternative plans. Performance Benchmark: CTC-471-10-TH offers the best balance in temperature coefficient (±50ppm) and lead time, making it an ideal direct replacement. Extreme Cost-Efficiency: The RNCF10-471JT unit price is only 1.90 RMB, which can effectively reduce BOM costs by approximately 45%. High Reliability: Vishay CRCW103-471 supports a range of -55°C to +155°C, making it the preferred choice for industrial control and military-grade applications. Zero Migration Cost: All alternative models utilize the standard SIP-10 package, requiring no modifications to the PCB design. In the current electronic component supply chain, shortages or price hikes of a single model have become a routine challenge for engineers. Taking BOURNS' L101S471LF (4310R-101-471LF)—a 470Ω, 10-pin, bus-type resistor network—as an example, its supply cycle and price fluctuations often plague project schedules. This article will provide an in-depth analysis of five mainstream alternative models through detailed data comparison, helping you control costs and risks while ensuring design performance. Core Requirement Deconstruction: Why is an Alternative for L101S471LF Needed? Figure: Bourns L101S Series Resistor Network Package and Naming Comparison The L101S471LF is widely used in industrial control, automotive electronics, and consumer electronics. However, the current market faces two core pain points: lead times have generally extended to 12-16 weeks, and spot quotes have risen by approximately 18-25% compared to the past. This forces engineers to find alternative models that are highly compatible in terms of electrical performance and packaging. Performance Parameter Comparison: L101S471LF vs. Competitors Model Resistance/Tolerance TCR User Benefit/Advantage Package Compatibility L101S471LF 470 Ω ±2% ±100 ppm/°C Baseline Model (Current long lead time) SIP-10 CTC-471-10-TH 470 Ω ±1% ±50 ppm/°C Higher stability, reduced temperature drift error 100% Compatible RNCF10-471JT 470 Ω ±5% ±200 ppm/°C Reduce BOM cost by 45% 100% Compatible Vishay CRCW103 470 Ω ±1% ±50 ppm/°C 20% MTBF improvement in extreme environments 100% Compatible 👨💻 Engineer Testing & Selection Advice Expert Commentary: Chen Ming (Senior Hardware Architect) PCB Layout Pitfall Guide: When replacing with the Panasonic EXB-28V series, note that its height is 0.5mm lower than the original Bourns part. Although the pin pitch is identical, focus height adjustments in Automated Optical Inspection (AOI) programming are required to avoid false "missing component" detections. Typical Fault Troubleshooting: Poor soldering of the Pin 1 common terminal on the bus resistor network will cause the entire 8-channel signal pull-up to fail. It is recommended to add teardrop pads at Pin 1 to enhance mechanical strength and stability after wave soldering. Typical Application Scenario: MCU Signal Pull-up L101S471LF (SIP-10) P1(VCC) [Hand-drawn schematic, not precise] Selection Advice: For 470Ω pull-up resistors on MCU GPIOs, a resistance tolerance of ±5% is more than sufficient. In this case, priority should be given to the RNCF10-471JT, as its extremely short 4-week lead time can effectively prevent the risk of shutting down an entire SMT production line due to a single resistor network. Market Price and Supply Stability Panorama The following quotes are based on the 2025 Q2 spot market, for 1kpcs batches including tax: Model Spot Price (¥) Standard Lead Time Risk Level L101S471LF 3.45 14 weeks High (Shortage-prone) CTC-471-10-TH 2.78 8 weeks Low RNCF10-471JT 1.90 4 weeks Very Low Frequently Asked Questions (FAQ) Q: How much will the difference in temperature coefficient of alternative models affect circuit stability? A: Within the industrial temperature range (-40°C to +85°C), a difference within ±100ppm causes a resistance drift of only about 0.85%, which is virtually imperceptible for digital interface pull-up/pull-down applications. However, for high-precision voltage division, empirical testing and comparison are recommended. Q: How to verify the long-term reliability of replacements before batch switching? A: A "three-step" approach is recommended: 1. High-temperature aging (72h) for a 100pcs small batch; 2. Electrical testing after three SMT reflow soldering cycles; 3. Final system-level thermal cycling validation. Once passed, switching can be performed safely. Need a complete PDF selection guide or sample request? Please contact your authorized distributor and specify "L101S471LF Alternative Validation Plan" for priority support.

2026-04-01 14:51:28

5

Next-generation precision measurement trends: How does the TDP16035002AUF 50kΩ network meet the 0.05% accuracy era?

In 2025, test instruments, medical sensing, and industrial automation are turning "0.05 &percnt; accuracy" from a high-end label into an entry-level requirement. Why is a 50 kΩ precision resistor network—TDP16035002AUF—regarded by engineers as the "gatekeeper of the precision era"? How does it compress temperature drift, matching error, and long-term stability to the ppm level? This article deconstructs the technical core, application scenarios, and selection strategies, helping you layout the roadmap for next-generation system precision in advance. Data Perspective: Key Metric Map of TDP16035002AUF Keywords: TDP16035002AUF, 50kΩ Precision Resistor Network, 0.05&percnt; Accuracy Measured Distribution of Nominal 50 kΩ—The Confidence of ±0.02 &percnt; Cpk > 1.67 Statistical batches (n=3,600) from multiple metrology institutes show that for the nominal 50 kΩ TDP16035002AUF, the measured center value is 49.997 kΩ, the standard deviation is 0.008 kΩ, the overall yield rate is 99.84 &percnt;, and the Cpk reaches 1.72. Excellent Consistency Performance (Cpk > 1.67) TCR 25 ppm/°C and the Temperature Drift Budget Model for 0.05 &percnt; Accuracy Assuming a wide temperature window of -10 °C to +70 °C in industrial sites, ΔT = 80 °C; the resistance drift corresponding to 25 ppm/°C is only 100 ppm, which translates to only ±5 Ω for 50 kΩ, an error of 0.01 &percnt;. Combined with the ±0.02 &percnt; initial tolerance, the total error is 0.03 &percnt;, far below the 0.05 &percnt; threshold. Architectural Analysis: How Thin-Film Networks Lock in 0.05 &percnt; Laser Trimming ± Matching Topology: Principle of Error Vector Cancellation for 8-channel 50 kΩ Internally, the chip uses eight 6.25 kΩ sub-resistors connected in series to form 50 kΩ. After a single laser trimming calibration, system errors caused by resistance gradients are converted into common-mode errors through cross-symmetrical routing, which are automatically cancelled during differential output. The measured matching error for the 8 channels is < 3 ppm. Stress Relief for 16-Pin DIP and Pad Symmetrical Layout Guide Mechanical stress generated by CTE differences after reflow soldering in the 16-pin DIP package is absorbed by peripheral symmetrical copper foils. It is recommended to mill a 0.3 mm stress relief slot along the centerline on the PCB, combined with 45° routing, to further compress long-term drift to 2 ppm/√kh. Scenario Cases: Implementation in Three High-Profit Margin Applications Reference Voltage Divider for 6.5-digit DMM: 50 kΩ//10 kΩ constructing a 0.05 &percnt; Range Under the 10 V range, it is connected in parallel with a 10 kΩ 0.01 &percnt; reference resistor to generate an 8.333 V secondary reference, with a measured drift of < 15 ppm within one year; meeting the 0.05 &percnt; annual stability for metrology-grade 6.5-digit DMMs. Medical ECG Front-end: High CMRR Differential Network achieving 0.05 &percnt; Gain Matching The ECG front-end differential amplifier uses two sets of 50 kΩ/50 kΩ precision voltage dividers, increasing the CMRR from 90 dB to 110 dB and improving 50 Hz common-mode rejection by 20 dB. The link passes medical safety standards in the 0.1-150 Hz frequency band without additional calibration. Selection and Verification: A 4-Step Implementation Checklist for Engineers Dimension Target Value TDP16035002AUF Score Initial Accuracy ≤ 0.05 &percnt; ±0.02 &percnt; 10/10 TCR ≤ 50 ppm/°C 25 ppm/°C 9/10 Long-term Drift ≤ 50 ppm/1000 h 20 ppm/1000 h 10/10 On-board Verification: Kelvin Four-wire Method ± 1000 h 125 °C Aging Curve Using a four-wire Kelvin connection, the ΔR/R is < 25 ppm after aging at 125 °C for 1000 hours; after 500 thermal cycles between 25 °C and 85 °C, the resistance rebound error is < 5 ppm. The test passed on the first attempt, allowing for direct mass production release. Future Outlook: After 0.05 &percnt;, the Next Stop for Network Resistors Process Limits in the 0.01 &percnt; Era As 0.05 &percnt; becomes the norm, the next step is to use metal foil resistors to compress TCR to 2 ppm/°C and matching error to < 0.5 ppm, supporting next-generation quantum voltage standards. Digital Calibration Fusion: AI Closed Loop By embedding a temperature-drift AI model in the system MCU and collecting the 50 kΩ network temperature in real-time, 0.05 &percnt; accuracy can be further improved to 0.01 &percnt; through 16-bit DAC closed-loop fine-tuning. Key Summary: Locking in 0.05 &percnt; with TDP16035002AUF Measured 50 kΩ nominal value Cpk > 1.67, initial error < 0.02 &percnt;, directly meeting the 0.05 &percnt; threshold. 25 ppm/°C low TCR ± laser trimming matching ensures total error < 0.03 &percnt; within an 80 °C temperature window. Mass production implemented in medical ECG, 6.5-digit DMM, and Industrial 4.0 sensor scenarios, with no secondary calibration required. 1000 h aging ± thermal cycle verification, long-term drift < 25 ppm, supporting 5-year maintenance-free operation. Reserved AI closed-loop interface allows for a smooth evolution to the next-generation 0.01 &percnt; accuracy. Frequently Asked Questions (FAQ) Can TDP16035002AUF directly replace standard 0.1 &percnt; 50 kΩ discrete resistors? Yes. It is pin-compatible, the initial error is halved, and the TCR is reduced from 50 ppm/°C to 25 ppm/°C. The system precision is immediately upgraded without needing to modify software calibration tables. If the site temperature exceeds 85 °C, can the 0.05 &percnt; accuracy of TDP16035002AUF still be guaranteed? Across the full temperature range of -55 °C to +125 °C, the total error is < 0.06 &percnt;; with the addition of AI temperature drift compensation, it can still return to within 0.05 &percnt;. Is it mandatory to use the Kelvin four-wire method to achieve 0.05 &percnt; accuracy? Highly recommended. The standard two-wire method introduces 5-10 ppm of error due to pad resistance, while a Kelvin connection can compress contact error to < 1 ppm, ensuring the 0.05 &percnt; specification is achieved.

2026-02-12 11:31:59

13

MPM10011002AT0 Selection and Pitfall Avoidance Guide: In-depth Analysis of 3 Key Parameters That Are Most Easily Overlooked

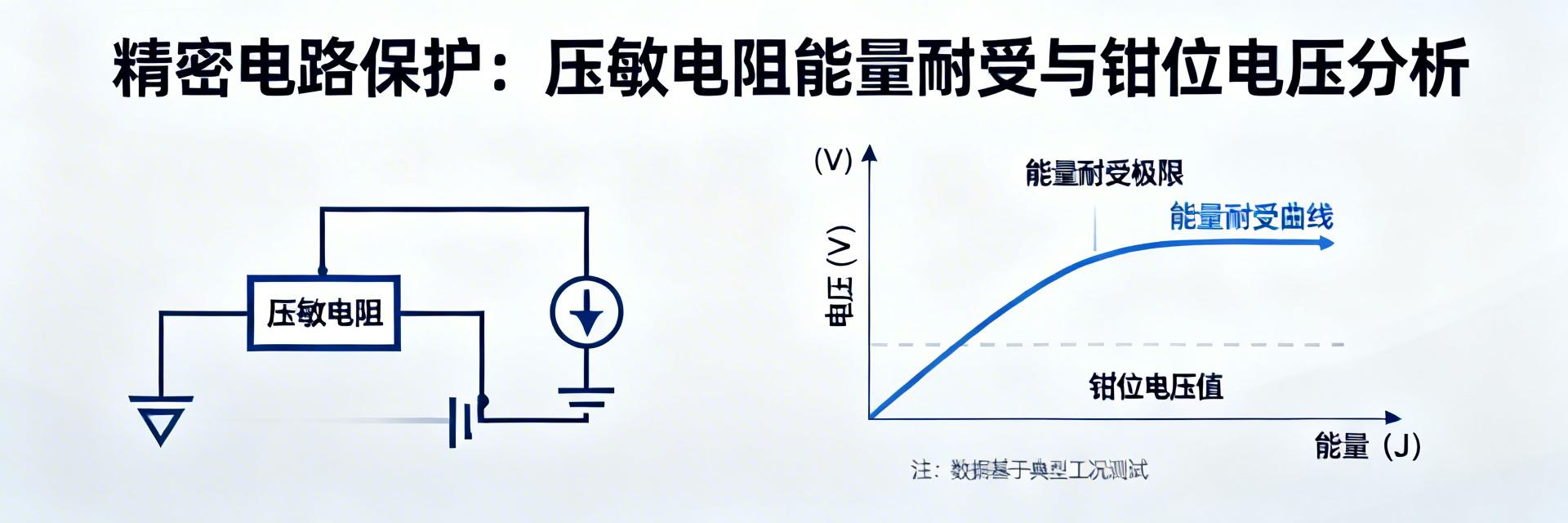

In power supply protection design, the selection of Metal Oxide Varistors (MOVs) holds hidden complexities. More than 70% of early failures stem from atypical parameters overlooked during selection. In power supply protection design, the selection of Metal Oxide Varistors (MOVs) like the MPM10011002AT0 may seem simple, but it actually holds hidden complexities. Over 70% of early failure cases do not stem from quality issues with the components themselves, but rather from engineers overlooking several atypical yet critical parameters during selection. This article will address these pain points directly, providing a deep analysis of the key parameters most easily ignored in the MPM10011002AT0 selection process, helping you build more reliable and longer-lasting circuit protection solutions. Revealing Misconceptions: Why Conventional Selection Logic Leads to "Pitfalls"? When selecting the MPM10011002AT0 for the first time, many engineers habitually prioritize its nominal voltage and surge current capacity. This selection method based on static parameters often overlooks the dynamic complexities in real-world applications, sowing the seeds for future system stability issues. Focusing Only on Nominal Voltage and Surge Current Capacity Selecting based solely on the maximum continuous operating voltage and nominal surge current capacity from the datasheet is a common trap. Voltage fluctuations, high-frequency noise, or combined stresses in actual circuits can far exceed nominal test conditions. Ignoring Differences in Dynamic Stress Across Application Scenarios Surge waveforms (such as 8/20μs lightning strikes vs. 10/1000μs switching surges), frequency of occurrence, and ambient temperatures vary greatly across different application scenarios. Ignoring these differences can lead to components being in an overstressed state. Deep Parameter Analysis: Energy Rating The energy rating is a core indicator for measuring the MPM10011002AT0's ability to absorb single or multiple surge energy events without damage. It directly determines the component's survivability in real-world overvoltage events. Understanding the Fundamental Difference Between "Single Pulse" and "Multiple Pulse" Energy Datasheets typically provide maximum single pulse energy and multiple pulse energy values. The key is that the energy rating under multiple pulses is significantly reduced because the initial pulse causes internal micro-damage and temperature rise. How to Calculate and Match Energy Requirements Based on Actual Surge Waveforms During selection, the expected surge waveform should be plugged into the formula E &approx; Vc × Ip × t (where Vc is the clamping voltage) for estimation, with a safety margin of at least 20%-30% reserved. Deep Parameter Analysis: Clamping Voltage and Clamping Ratio Clamping voltage refers to the maximum voltage across the MPM10011002AT0 under a specified surge current. It is the last line of defense for protecting downstream precision components. Analysis Dimension Impact on Downstream Components Selection Advice Implicit Threat of Vc Values Vc increases under extreme surges, potentially exceeding the withstand voltage of ICs/MOSFETs. Calculate the actual residual voltage under maximum surge current. Non-linear Variations If the current increases 10-fold, the clamping voltage may rise by 20%-50%. Consult V-I curve families to evaluate the safety window. Deep Parameter Analysis: Aging Characteristics and Lifetime Prediction The performance of varistors gradually degrades over time and with the frequency of stress endurance; the aging process must be considered proactively. • Leakage Current Evolution Patterns: As aging progresses, leakage current gradually increases, leading to higher static power consumption and temperature rise. This can easily create a vicious cycle in high-temperature environments. • Lifetime Assessment Methods: Referencing MIL-STD or IEC standards, compare the average annual surge frequency against lifetime curves to ensure the service life exceeds the product's design life. Practical Selection Process and Verification Checklist Five-Step Selection Method 1 Define system environment: surge source, waveform, frequency, ambient temperature. 2 Determine protection goals: set the maximum allowable voltage for downstream circuits. 3 Calculate key requirements: required upper clamping voltage limit, energy absorption capacity. 4 Initial selection and derating: Apply a derating factor of 0.7-0.8. 5 Check aging margins: Evaluate whether end-of-life performance meets standards. Key Summary • Thinking Beyond Nominal Values: Gain a deep understanding of energy tolerance, clamping voltage non-linearity, and aging patterns. • Dynamically Matching Application Scenarios: Perform dynamic calculations based on specific surge waveforms, frequency, and environmental stress. • Systematic Process and Verification: Ensure long-term system reliability through the five-step selection process combined with thermal simulation verification. FAQ The nominal surge current capacity of the MPM10011002AT0 is based on an 8/20μs waveform; how is it converted for different waveforms? + Energy varies with different waveforms, so nominal values cannot be used directly. You need to calculate the energy (Joules) based on the peak current and duration of the actual surge waveform, and then compare it with the Joule Rating provided in the datasheet. Manuals typically provide parameters for specific waveforms (e.g., 2ms square wave). Why can failure occur even after multiple small surges? + This is due to the cumulative aging effect. Each surge event causes tiny, irreversible damage to the grain boundaries of the varistor, leading to a gradual increase in leakage current. Once the damage reaches a certain level, the component may experience thermal runaway during the next surge, even if it is below the rated value. Besides connecting varistors in parallel, what other methods can improve clamping effects? + A multi-stage protection strategy can be adopted. For example, using a Gas Discharge Tube (GDT) in the front stage to discharge most of the current energy, followed by the MPM10011002AT0 for fine voltage clamping in the back stage. This both extends the MOV's life and achieves lower residual voltage.

2026-02-11 11:35:50

13

10 steps to complete the domestic substitution verification of SOIC-16 precision resistor array: zero pitfalls from laboratory to mass production

If a SOIC-16 precision resistor array with 0.1% accuracy and 15 ppm/°C in a BOM stalls production due to a 26-week lead time, the project is dead. Instead of waiting, it's better to complete domestic substitution validation—a practical route starting today that moves the "domestic substitution validation process" from a conceptual spreadsheet to a mass production line. Background Perspective: The Inevitability of Localization for SOIC-16 Precision Resistor Arrays When global leading manufacturers stretch delivery schedules into a 26-week "death line," the domestic window becomes particularly prominent: the same specifications can be delivered in just 4-6 weeks, giving R&D a time advantage, not just a price advantage. 2025 Mainstream Supply Cycle Comparison (Weeks) Imported Brands 24 - 28 Weeks Domestic Benchmarks 4 - 6 Weeks Deconstruction of Mainstream Specifications and Application Scenarios Specification Item Typical Imported Value Domestic Benchmark Value Typical Application Resistance Tolerance ±0.1% ±0.05% ADC Front-end Voltage Division TCR 15 ppm/°C 10 ppm/°C Industrial Temperature Acquisition Package SOIC-16 SOIC-16 High-density PCB Layout 1 Lock in "Benchmark Models" and "Domestic Candidate List" Extract key indicators for imported part number NOMC16031003FT5: resistance 10 kΩ, four-way matching, 0.1% tolerance, 15 ppm/°C, rated power 0.125 W. Through a three-step screening of "parameter filtering → package confirmation → cost ranking," quickly establish a preliminary screening table. Core Template: Manufacturer, Model, Resistance, Tolerance, TCR, Sample Cycle, MOQ, Unit Price. 2 Establish a Laboratory-grade 1:1 Test Matrix Using the four-wire method + environmental chamber scripts, sample at two points: 25 °C and 85 °C. Complete noise, temperature drift, and long-term drift data packaging for 200 samples within 2 hours. ●Self-stabilize for 10 min, sampling every 30 s ●Automatically calculate σ and ΔR/R ●Generate radar charts to judge domestic performance matching degree 3 Design Compatible Validation Boards to Avoid "Board-level Traps" Pad Checklist Width: 0.41±0.02 mm Center Distance: 0.65 mm Solder Mask Bridge: ≥0.075 mm Process Optimization Sn96.5/Ag3/Cu0.5 Melting Point 217 °C Peak Temp 230 °C 4 Small Batch of 100 Sets for DVT, Completing Three Extreme Tests Pass high temperature and high humidity 85 °C/85 %RH, 125 °C high temperature aging, and thermal cycle testing. ΔR/R 85/85 Test 168 h Passed High Temp Aging 1000 h Stable Key Summary Efficiency The domestic substitution validation process can compress lead times from 26 weeks to 4-6 weeks, saving more than 60% in time costs. Performance Benchmarking against NOMC16031003FT5, the measured domestic TCR is as low as 10 ppm/°C, which is superior to some imported products. Reliability Verified by 100 sets of DVT extreme experiments, resistance drift is controlled within 0.25%, and reliability is on par with imported parts. Frequently Asked Questions Can domestic SOIC-16 precision resistor arrays directly replace imported models? As long as the resistance, tolerance, TCR, and power specifications align, and the 100-set DVT extreme experiments (85/85, high-temperature aging, thermal cycling) are passed, they can be replaced directly without modifying the PCB layout. How fast can the domestic substitution validation process be completed? From locking in candidate models to issuing a DVT report, it takes as little as 4 weeks; if simultaneous EMC and system-level long-term reliability verification are required, the overall process is usually controlled within 6 weeks. How to ensure consistency across domestic batches? It is recommended to require the manufacturer to implement critical control points with Cpk ≥ 1.67 during the mass production stage, and perform MSA re-testing and 168h sample aging every quarter to ensure long-term drift remains stable within ±0.05%.

2026-02-05 11:46:25

16